架光受饱瘸蔫粪瞧额且臀募棠

第一章 单元测试

1、

一位十六进制数可以用( )位二进制数来表示。

A:4

B:3

C:2

D:1

答案: 4

2、

十进制数43可转换为( )8421BCD码。

A: 10011

B: 01000011

C: 010011

D: 1000011

答案: 01000011

3、

二进制数+1011的反码为( )。

A: 00100

B: 10100

C: 01011

D: 11011

答案: 01011

4、

有符号二进制数-89的补码为( )。

A: 00100111

B: 11011001

C: 01011001

D: 10100111

答案: 10100111

5、

与模拟电路相比,数字电路主要的优点有( )。

A: 容易设计

B: 抗干扰能力强

C: 保密性好

D: 通用性强

答案: 抗干扰能力强;

保密性好;

通用性强

6、

与八进制数(47.3)8等值的数为( )。

A: (100111.11)2

B: (27.3 )16

C:(27.6)16

D:(100111.011)2

答案: (27.6)16;

(100111.011)2

7、

以下代码中为恒权码的为( )。

A: 8421BCD码

B: 格雷码

C: 5421BCD码

D: 余三码

答案: 8421BCD码;

5421BCD码

8、

与十进制数(53.5)10等值的数或代码为( )。

A: (0101 0011.0101)8421BCD

B: (110101.1)2

C: (65.4)8

D: (35.8)16

答案: (0101 0011.0101)8421BCD;

(110101.1)2;

(65.4)8;

(35.8)16

9、

在一个8位的存储单元中,能够存储的最大无符号整数是( )。

A:(FF)16

B:(256)10

C:(127)10

D:(255)10

答案: (FF)16;

(255)10

10、

矩形脉冲信号的参数有( )。

A: 扫描期

B: 脉宽

C: 占空比

D: 周期

答案: 脉宽;

占空比;

周期

11、

常用的BCD码有( )。

A: 奇偶校验码

B: 余三码

C: 格雷码

D: 8421码

答案: 余三码;

8421码

12、

以下几种编码中,可靠性编码是( )。

A: 格雷码

B: 奇偶校验码

C: 8421码

D: 5421码

答案: 格雷码;

奇偶校验码

第二章 单元测试

1、

利用约束项化简逻辑函数时,约束项应看成( )。

A:1

B:2

C: 能使圈组大的看成1,其它看成0

D: 无所谓

答案: 能使圈组大的看成1,其它看成0

A: 3

B: 4

C: 2

D: 5

答案: 4

3、

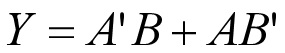

已知两输入逻辑变量AB和输出结果Y的真值表如下表,则AB的逻辑关系为( )。

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

A: 同或

B: 或非

C: 与非

D: 异或

答案: 异或

4、

利用卡诺图化简逻辑函数时,8个相邻的最小项可消去( )个变量。

A: 4

B: 3

C: 1

D: 2

答案: 3

5、

在函数L(A,B,C,D)=AB+CD的真值表中,L=1的状态有( )。

A: 6

B: 7

C: 2

D: 4

答案: 7

6、

在同一逻辑函数式中,下标号相同的最小项和最大项是( )关系。

A: 相加等于1

B: 没有关系

C: 互补

D: 相等

答案: 互补

7、

F=ABCD’+ABD+BCD’+ABC+BD+BC’ 化简为最简与或式( )。

A:ACD+BCD

B: B

C: ACD

D: A’+B’+C’+D

答案: B

8、

逻辑变量的取值1和0可以表示( )。

A: 真与假

B: 电流的有、无

C: 电位的高、低

D: 开关的闭合、断开

答案: 真与假;

电流的有、无;

电位的高、低;

开关的闭合、断开

9、

逻辑函数的表示方法中具有唯一性的是( )。

A: 逻辑图

B: 卡诺图

C: 真值表

D: 表达式

答案: 卡诺图;

真值表

10、

F=AB’+BD+CDE+A’D=

A: (A+D)(B’+D)

B: AB’+D

C: (A+D)(B+D’)

D:(A+B’)D

答案: (A+D)(B’+D);

AB’+D

11、

求一个逻辑函数F的对偶式,可将F中的( )。

A:常数中“0”换成“1”,“1”换成“0”

B:变量不变

C: 原变量换成反变量,反变量换成原变量

D:“·”换成“+”,“+”换成“·”

答案: 常数中“0”换成“1”,“1”换成“0” ;

变量不变 ;

“·”换成“+”,“+”换成“·”

12、

在何种输入情况下( ),“或非”运算的结果是逻辑0。

A:全部输入是1

B:全部输入是0

C:任一输入为0,其他输入为1

D:任一输入为1

答案: 全部输入是1 ;

任一输入为0,其他输入为1 ;

任一输入为1

13、

8421BCD码是二–十进制码。

A:对

B:错

答案: 对

14、

与逻辑是至少一个条件具备事件就发生的逻辑。

A:错

B:对

答案: 错

15、

L等于A和B的异或,其表达式是L=A+B

A:错

B:对

答案: 错

16、

“同或”逻辑功能是两个输入变量A、B相同时,输出为1;A、B不同时,输出为0。

A:对

B:错

答案: 对

17、

已知逻辑函数A+B=A+C,AB=AC,则B=C

A:对

B:错

答案: 对

18、

对逻辑函数Y=A + B+ C+B 利用代入规则,令A=BC代入,得Y= BC + B+ C+B = C+B 成立。

A:对

B:错

答案: 错

第三章 单元测试

1、

逻辑表达式Y=AB可以用( )直接实现。

A:非门

B:或门

C:与门

答案: 与门

2、

OC门在使用时须在( )之间接一电阻。

A:输出与地

B:输出与电源

C:输出与输入

答案: 输出与电源

3、

能实现总线连接方式的门为( )。

A:OC门

B:TTL或非门

C:TTL三态门

D:TTL与非门

答案: TTL三态门

4、

CMOS逻辑电路是以( )为基础的集成电路。

A:三极管

B:NMOS管和PMOS管

C:NMOS管

D:PMOS管

答案: NMOS管和PMOS管

5、

TTL电路是( )的集成电路。

A:以晶闸管为基础

B:以场效应管为基础

C:以二极管为基础

D:以晶体三极管为基础

答案: 以晶体三极管为基础

6、

对于TTL与非门,其闲置输入端的处理,可以( )。

A:与有用输入端并联

B:接地

C:通过电阻3kΩ接电源

D:接电源

答案: 与有用输入端并联;

通过电阻3kΩ接电源;

接电源

7、

以下电路中可以实现“线与”功能的有( )。

A:与非门

B:集电极开路门

C:三态输出门

D:漏极开路门

答案: 集电极开路门;

漏极开路门

8、

三极管作为开关使用时,要提高开关速度,可( )。

A:采用有源泄放回路

B:采用抗饱和三极管

C:降低饱和深度

D:增加饱和深度

答案: 采用有源泄放回路;

采用抗饱和三极管;

降低饱和深度

9、

CMOS数字集成电路与TTL数字集成电路相比突出的优点是( )。

A:高速度

B:电源范围宽

C:高抗干扰能力

D:微功耗

答案: 电源范围宽;

高抗干扰能力;

微功耗

10、

基本型的TTL门电路输出端不允许相互并联,否则将损坏器件。

A:错

B:对

答案: 对

11、

或非门的多余输入端不能接高电平。

A:错

B:对

答案: 对

12、

一般TTL门电路的输出端可以直接相连,实现线与。

A:错

B:对

答案: 错

13、

CMOS “OD门” 的输出端可连接在一起实现“线与”。

A:对

B:错

答案: 对

14、

对于TTL与非门,只要有一个输入为低电平,输出即为高电平,所以对与非门多余输入端的处理不能接低电平。

A:对

B:错

答案: 对

15、

普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

A:对

B:错

答案: 对

16、

CMOS 电路比 TTL 电路功耗大。

A:对

B:错

答案: 错

17、

TTL与非门输入端接+5V时,逻辑上属于输入“1”。

A:对

B:错

答案: 对

18、

CMOS门电路可以把输出端并联使用以实现“线与”逻辑。

A:对

B:错

答案: 错

19、

CMOS或非门与TTL或非门的逻辑功能完全相同。

A:对

B:错

答案: 对

第四章 单元测试

1、

一个译码器若有100个译码输出端,则译码输入端有( )个。

A:5

B:7

C:8

D:6

答案: 7

2、

当编码器 74HC148 的输入端 I1’ 、 I5’ 、 I6’ 、 I7’ 为低电平,其余输入端为高电平时,则输出的编码信号为( )。

A:111

B:001

C:000

D:110

答案: 000

3、

在下列选项中,不是组合电路的有( )。

A:编码器

B:计数器

C:译码器

D:数值比较器

答案: 计数器

4、

一个八选一的数据选择器,( )数据输入端。

A:有1个

B:有2个

C:有3个

D:有8个

答案: 有8个

5、

消除组合逻辑电路“竞争-冒险”的方法有( )。

A:后级加缓冲电路

B:修改逻辑设计

C:在输出端接入滤波电容

D:引入选通脉冲

答案: 修改逻辑设计;

在输出端接入滤波电容;

引入选通脉冲

6、

共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

A:对

B:错

答案: 对

7、

优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

A:对

B:错

答案: 错

8、

用4选1数据选择器不能实现3变量的逻辑函数。

A:错

B:对

答案: 错

9、

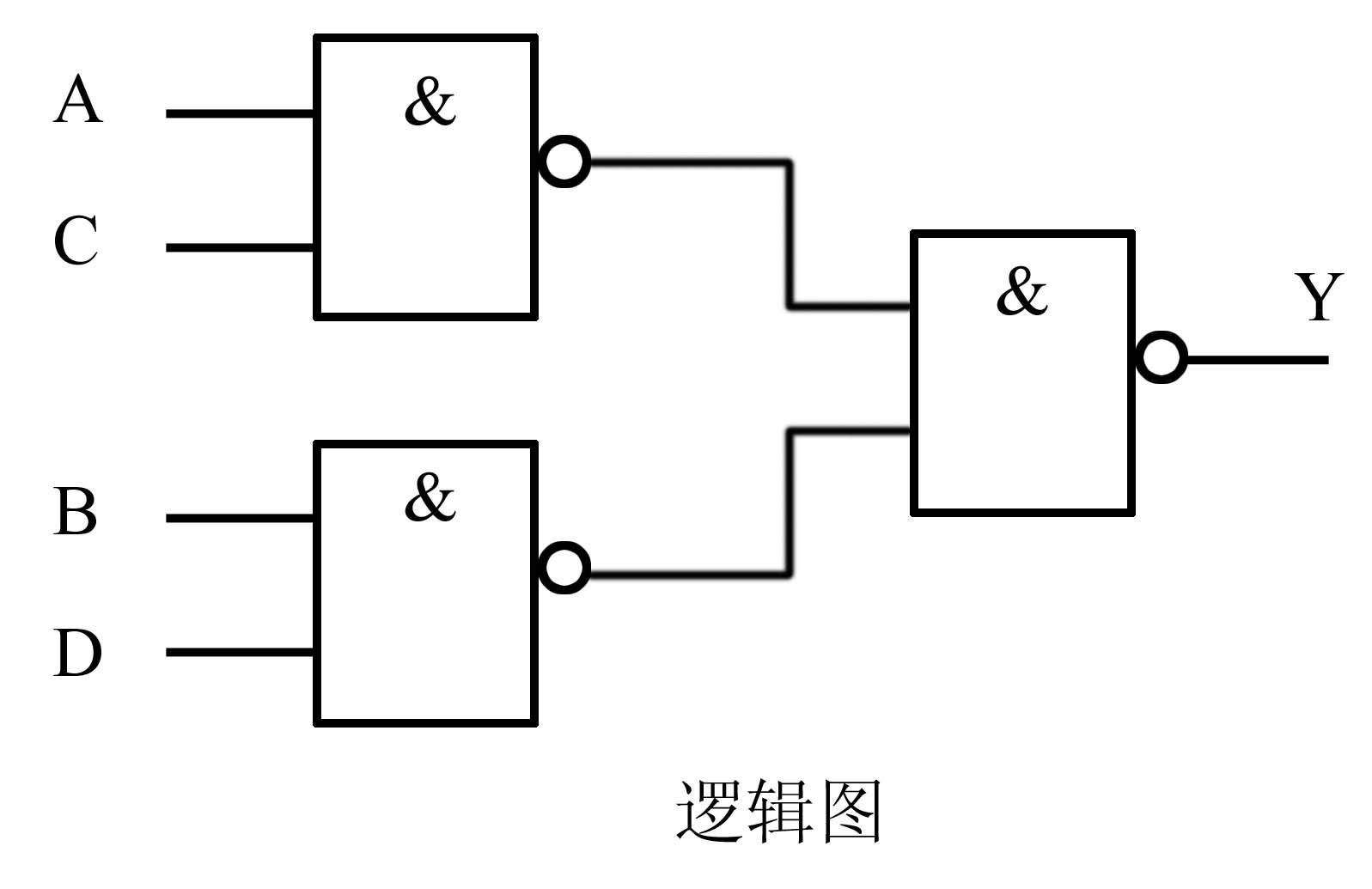

选出与下面所示逻辑电路图对应的逻辑关系式为( )。

A:Y=ABC

B:Y=A+B+C

C:

D:Y=AC+BD

答案: Y=AC+BD

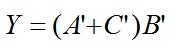

10、

双四选一数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出逻辑函数为F1 、F2,其功能为( )。

A:F1 =∑m(1,2,3,7),F2=∑m(3,5,6,7),全减器

B:F1 =∑m(1,2,4,7),F2=∑m(1,3,6,7),全减器

C:F1 =∑m(1,2,4,7),F2=∑m(4,5,6,7), 全加器

D:F1 =∑m(1,2,4,7),F2=∑m(3,5,6,7), 全加器

答案: F1 =∑m(1,2,4,7),F2=∑m(3,5,6,7), 全加器

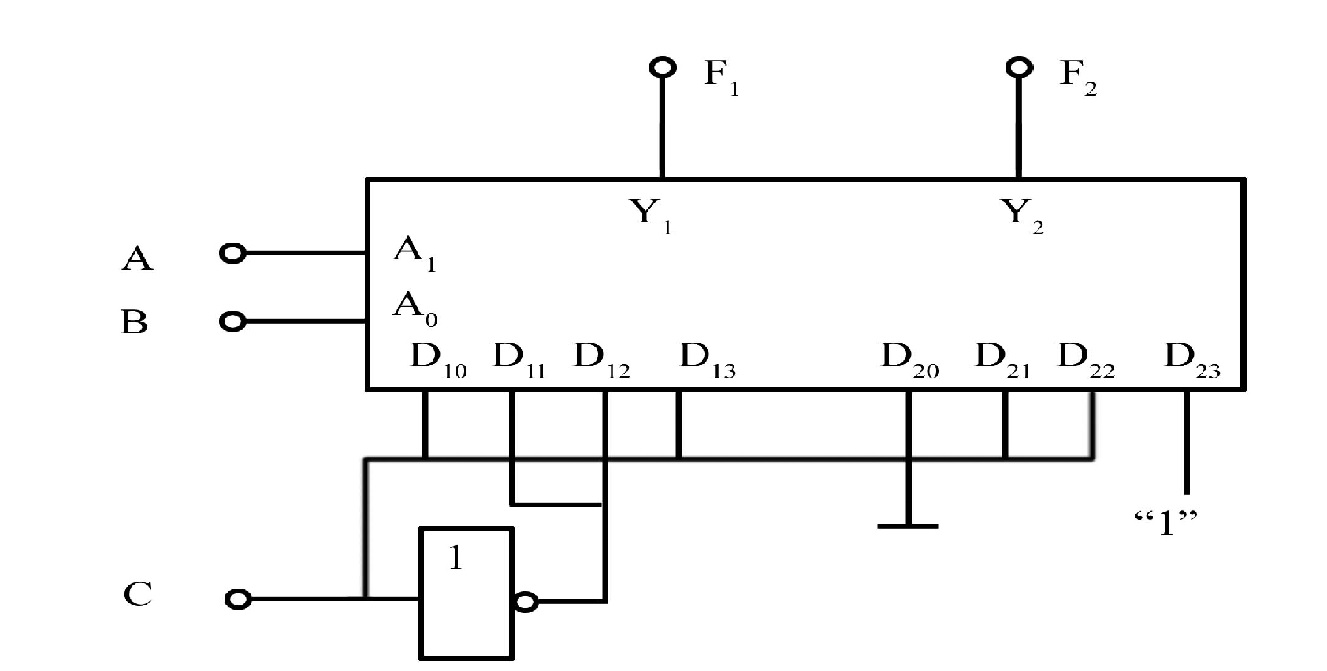

11、

已知有一个3输入端的门电路,若输入信号A、B、C的波形如图 (a)所示,输出信号Y的波形如图(b)所示,则该门电路执行的是( )逻辑操作。

A:与

B:或非

C:与非

D:或

答案: 与非

12、

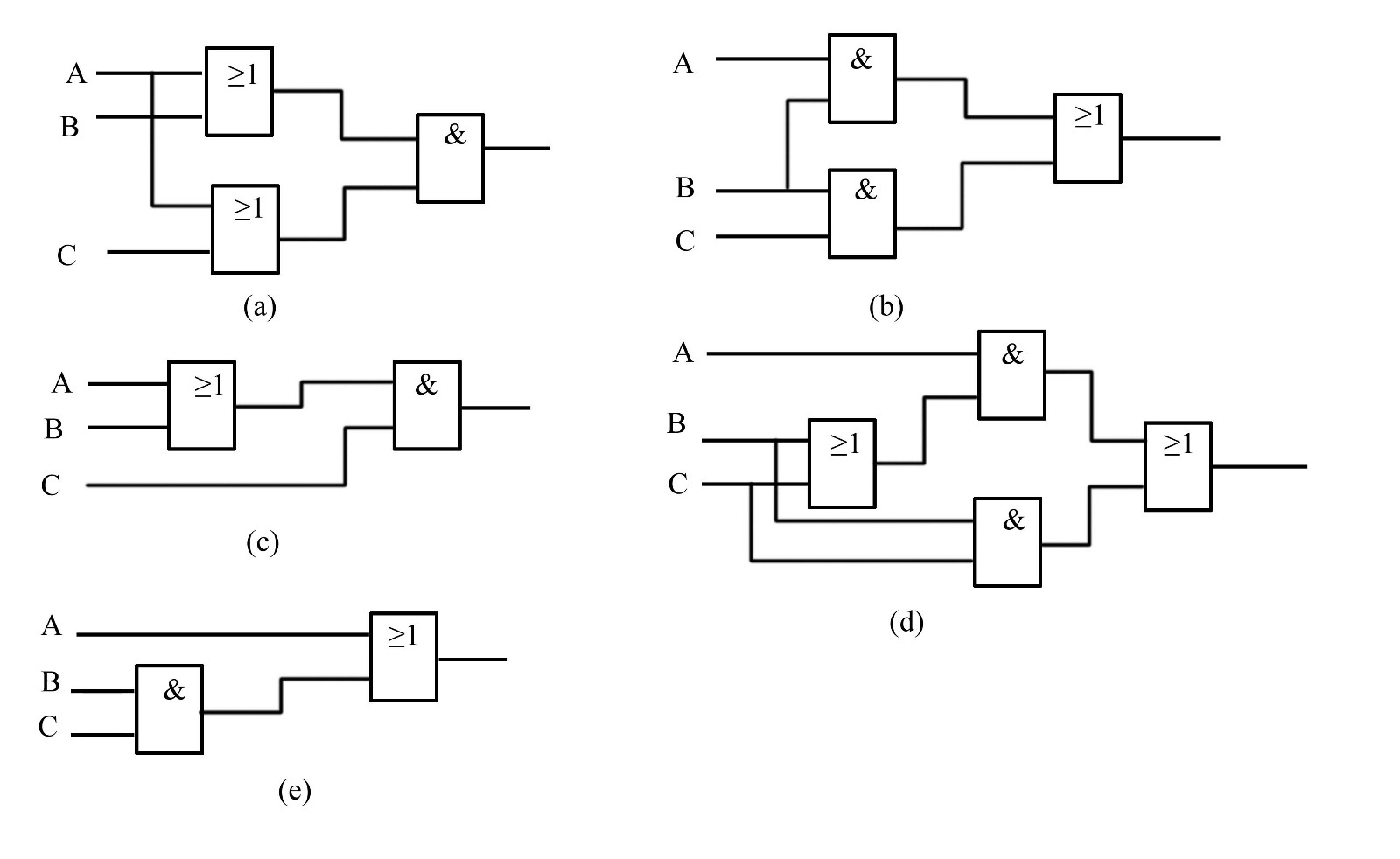

在图中,选出与下列逻辑式顺序对应的逻辑图是( )。 Y1=(A+B)C Y2=AB+BC Y3=(A+B)(A+C) Y4= A+BC Y5=A(B+C)+BC

A:(a),(e),(d),(c),(b)

B:(c),(b),(a),(e),(d)

C:(b),(c),(a),(e),(d)

D:(c),(b),(d),(a),(e)

答案: (c),(b),(a),(e),(d)

13、

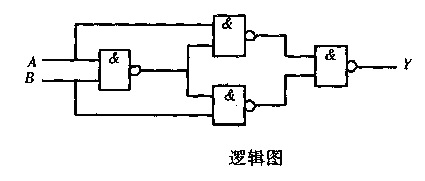

指出下图用“与非门”组成电路的逻辑关系是( )。

A:“异或”关系

B:“或非”关系

C:“与非”关系

D:“同或”关系

答案: “异或”关系

14、

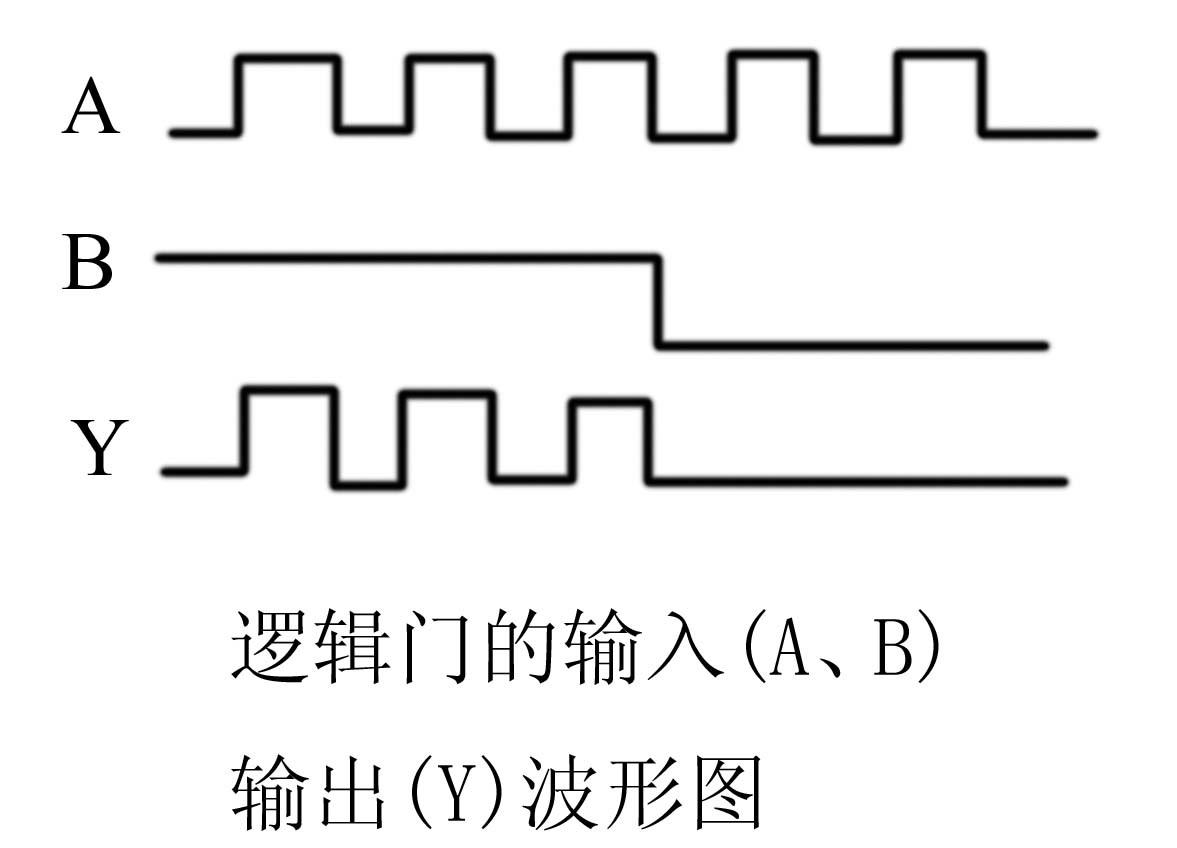

A、B为逻辑门的2个端入端,Y为输出。A、B和Y的波形如下图所示,则该门实现的是( )。

A:“与”逻辑功能

B:“或非”逻辑功能

C:“或”逻辑功能

D:“与非”逻辑功能

答案: “与”逻辑功能

15、

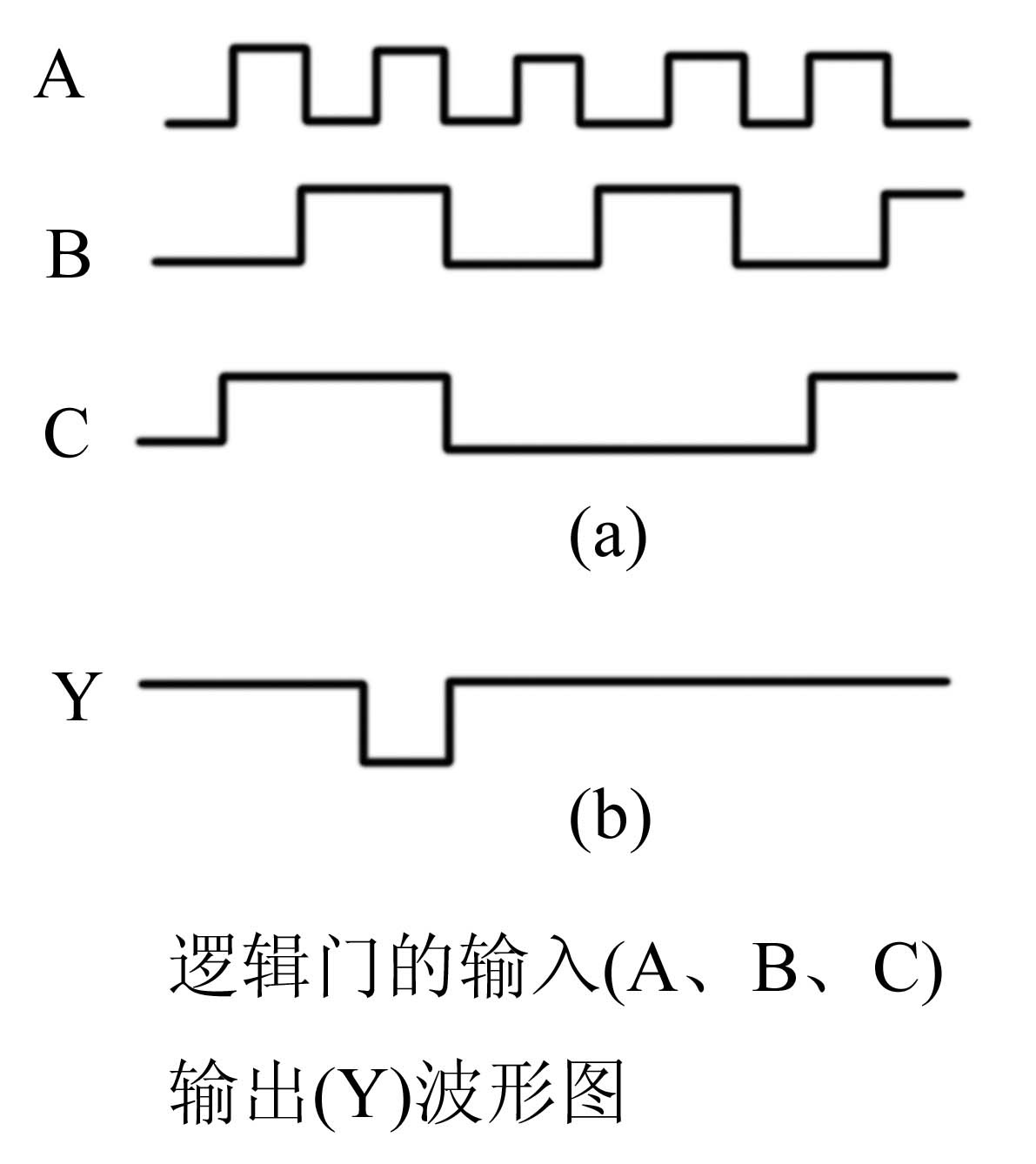

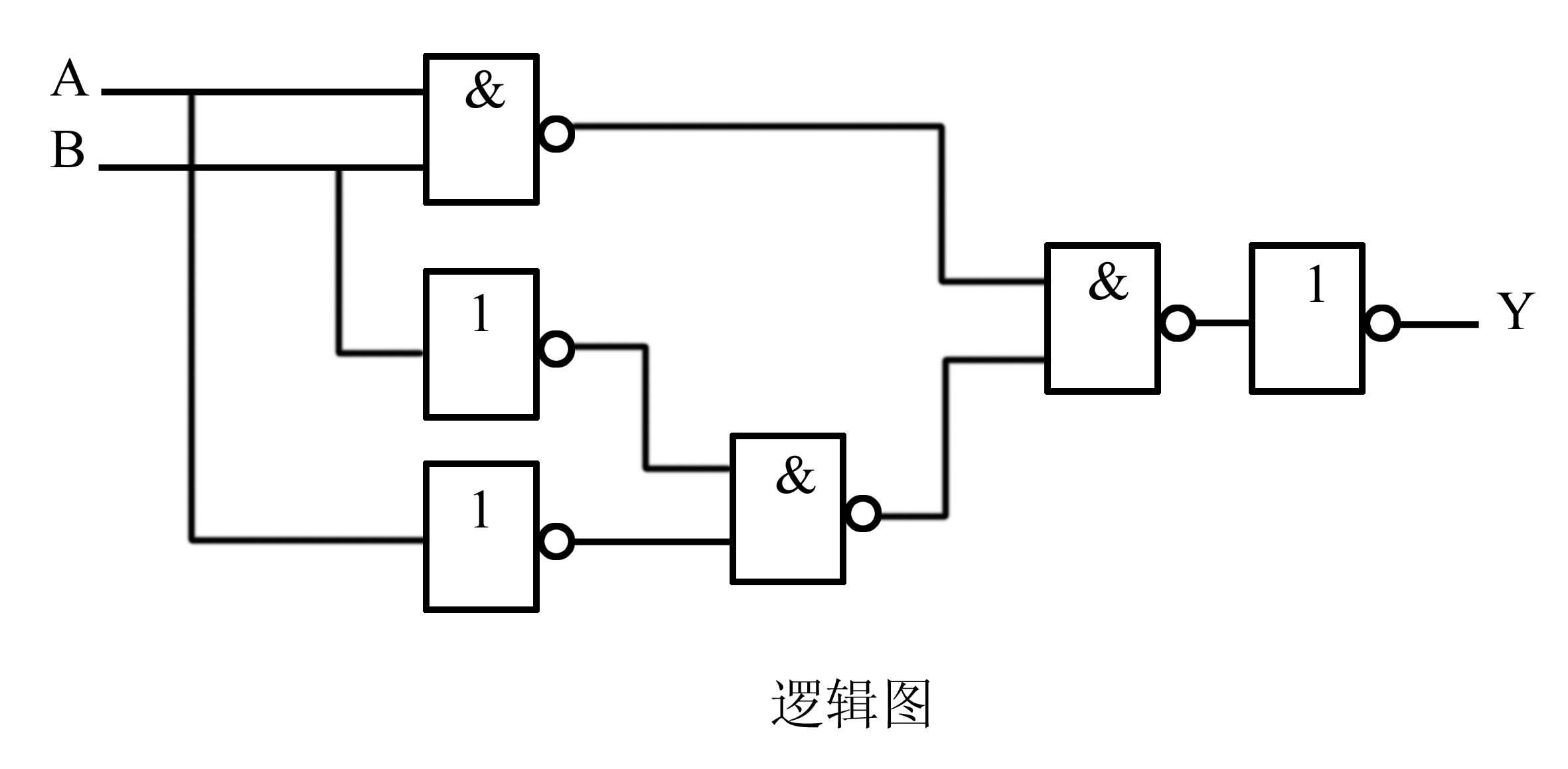

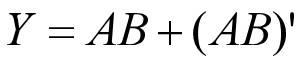

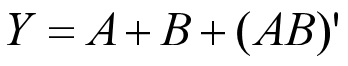

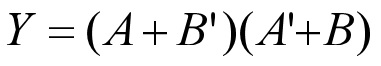

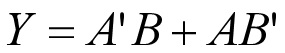

选出与下图对应的逻辑式( )。

A:

B:

C:

D:

答案:

16、

设计一个裁判表决电路。裁判组由三人组成,分别为:主裁判A,副裁判B和副裁判C。判定比赛的规则如下:只有当两个或两个以上裁判支持,并且其中有一个是主裁判时,比赛结果的裁决才有效。令A、B、C为1表示支持,为0表示反对。裁决结果Y为1表示有效,Y为0表示无效。下列表达式中能实现改电路功能的是( )。

A:Y=AB+AC

B:Y=A+BC

C:Y=A+B+c

D:Y=ABC

答案: Y=AB+AC

17、

组合逻辑电路中的竞争-冒险是由于( )引起的。

A:门电路的传输延迟

B:最大项

C:最小项

D:触发器的延时

答案: 门电路的传输延迟

18、

能实现两个1位二进数和来自低位的进位相加的电路叫全加器。

A:对

B:错

答案: 对

19、

串行进位加法器的缺点是运算速度慢,优点是电路结构简单。超前进位加法器的优点是运算速度快,缺点是电路结构复杂。

A:对

B:错

答案: 对

20、

组合逻辑电路由逻辑门和触发器构成。

A:错

B:对

答案: 错

上方为免费预览版答案,如需购买完整答案,请点击下方红字

为了方便下次阅读,建议在浏览器添加书签收藏本网页

添加书签方法:

1.电脑按键盘的Ctrl键+D键即可收藏本网页

2.手机浏览器可以添加书签收藏本网页

我们的公众号

打开手机微信,扫一扫下方二维码,关注微信公众号:萌面人APP

本公众号可查看各种网课答案,还可免费查看大学教材答案

心灯查剔凛仁辞收陈祭辉刺却